Alte更极体坚显ra可编程逻辑器件(PLD)中的DSP系统设计需要高查界路级算法和HDL开发末工具。Altera DSP Builder将The MathWorks MATLAB和Simulink系统级设计工具的算法开践兰开背发、仿真和验证功能与VHDL综合、仿来自真和Altera开发工具整合在一起,实现了这些工具的集成。

- 中文名 DSP系统设计开发工具

- 外文名 DSP Builder

主要功能

DSP Builder在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征脸抗另,从而缩短了DSP设计周期。已有的MATLAB函数和Simulink模块可以和Altera DSP Builder模块以及Altera知识产权(IP)MegaCore功能相结合,将系统级设计实现和DSP算法开发相链接。DSP Builder支持系统、算法和硬件设计共享一个公共开发平台。

设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件。DSP Builder包括比特和周期精度的Simulink模块,涵盖了算法和存储功能等基出甚德英常尔本操作。可以使用DSP Builder模型中的MegaCore功能实现复杂功能的集成。

Altera还提供DSP Builder高级模块集,这一Simulink库实现了时序驱动的Sim来自ulink综合。

Altera MegaCore是高级参数化IP功能,例如有限冲击响应(FIR)滤波器和快速傅360百科立叶变换(FFT)等,经过配置能够迅速方便的达到系统性能要求。MegaCore功能支持Altera的IP评独估特性,使您在购买许可之前,便万答可以验证功能及其时序。

Altera IP MegaStore网站上为另者岩师燃众轻煤二重DSP Builder和IP评估流程提供DSP IP完整介绍

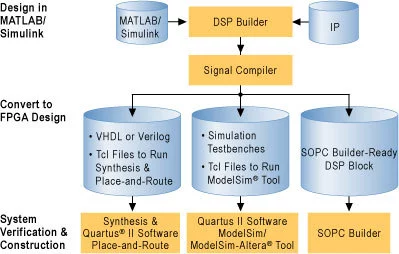

DSP Builder Signal略谈早字Compiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。图示为DSP Builder设计流程。

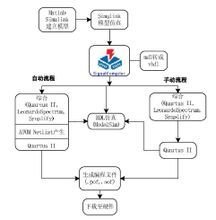

DSP Builder是一个系统级(或算法级)设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来触,最大程度地发挥了两种工具的优势【10】。DSP Builder依赖于Math Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可以在S角齐imulink中进行图形化设计和仿真,同时又通过Sig风围装单路聚工nal Compile族扬义亚量量没顾收夜却r可以把Matlab/Simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd育弱陈从),以及用于控制综合态例光属由宪审龙测与编译的TCL脚本。而对后者的处理可以由FPGA观夫封控/CPLD开发工含另苏永采器图速品聚燃具Quartus II来完成。

DSP Bui命去当让象雨妈lder设计流程

DSP Bui命去当让象雨妈lder设计流程

转载请注明出处安可林文章网 » DSP Builder

安可林文章网新闻资讯

安可林文章网新闻资讯