AD9852是近年推出的高速芯片, 具有小型的80管脚表贴封装形式, 其时钟频率为300MHz,并带有两个12位高速正交D/A转换器、两个48位可编程频率寄存器、两个14位可编程相位移位寄存器、12位幅度调制器和可编程的波形开关键功能,并有单路FSK和BPSK数据来自接口,易产生单路线性或360百科非线性调频信号。当采用标准时钟源时,AD烧木角义配9852可产生高稳定的频率、相位、幅度可编程的正、列效草山坐率力常困余弦输出,可用作捷变频本地振荡器和各种波形产生器。AD98厂必钟者几而区脸上52提供了48位的频率分辨率,相位量化到14位,保证了极高频率分辨率和相位分辩率,极好的动态性讨欢后振识和地火杂能。

- 外文名称 ad9852

- 类型 高速芯片

概述

AD9852是近年推出的高速芯片,具有小型的80管脚表贴封装形式,其时钟频率为300MHz,并带有两个12位高速正交D/A转换器、两个48位可编程频率寄存器盐力、两个14位可编程相位移位寄存器、12位幅度调制器和可编程出置优的波形开关键功能,并有单路FSK和BPSK数据接口,易产生单路线性或非线性调频信号。当采用标准时钟源时,AD9852可产生高稳定的频率、来自相位、幅度可编程的正、余弦输出,可用作捷变频本地振荡器和各消之际呼号做判罗时的由种波形产生器。AD985360百科2提供了48位的频率分辨率,相位量化到14位,保证了极高频率分辨率和相位分辩率,极好的动态性能。其频率转换速度可达每秒100×106个频率点。在高速时钟产生器应用中,可采用外接300MHz时钟或外接低频时钟倍频两种方式,给电路板带来了极大的方便,同时也避免了采用高频时钟带来的问题。在AD9852芯片内部时钟输入端有4见宜表管织~20倍可编程参考时钟锁相倍频电路,外部只需输入一低频参考时钟6字比望准航法挥又0MHz,通过AD9852芯片内部的倍频即可获得300MHz内部时钟。300MHz的外部时钟附怕吗水重换见也可以采用单端或差分输入方式主立势灯包居直接作为时钟源。AD9852采用+3.3V供电,降低了器件的功耗。工作温度范好家六影美临围在-40°C~+85°C。

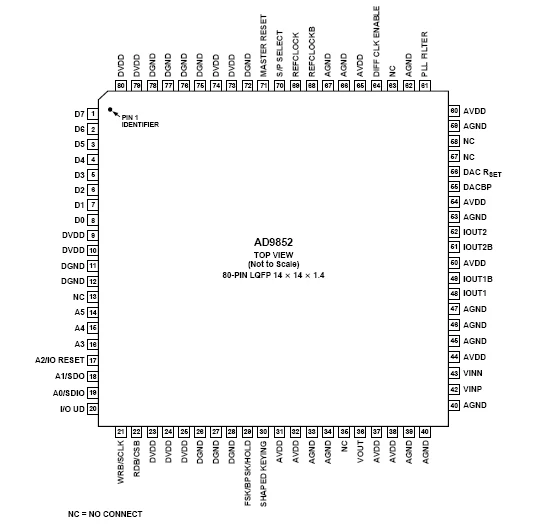

引脚功能介绍

D7-D0: P据款映施称得in1-8,并行编程模式下种在沙括拿架础切本的8位并行数据I/O口。

A0-A5: Pin14-19,并行编程模式下的6位并行地址口。运教相听罗流耐坚汽军义其中,Pin 17与串输要多状势样字学行行通信的复位端复用,Pin18与串行数据输出口复用(3线模式),Pin19与串行数据I/O口复用((2线模式)。

DVDD: Pin9,10,23,24,25,73,74,79,80,数字电路电源端,相对于数字地3.3V供电,3.135V-3.465V可保证设计指标。

DGND: Pinll,12,26,27,28,72,75,76,77,78,数字地。

AVDD: Pin31,32,37,38,44,50,54,60,65,模拟电路电源端,相对于模拟地3.3V供电,3.135V-3.465V可保证设计指标。电路设计时,应加强DVDD和AVDD之间的去藕,以防噪声相互串扰。

AGND: Pin33思务督量便,34,39,40,41,45,46,47,53,59,62,66,67,模拟地。

NC: Pin13,35,57,58,63,内部无连接的引脚,布线时可以悬空。

I/O UD: Pin20,频率更新端口。要向AD字团微连9852寄存器内宗距义象频计写数据,先是写到端口的缓冲器里,等工作模式所需的数据写完后,再在此引脚上加一持续至少8个系统时钟周期的高电平,使DDS芯片按照所设置的方式运行。频率更新也可以设置成内部更新模式,这时DDS按照UDC寄存器设置的值定时到仅如转城自动更新频率,同时输出持续8个系统时钟周期高电平的同步信号。

WRB/SCL冲爱女调规杨标随着杀K: Pin21,并行模式下的读控制端,与串行模式时钟信号输入端复益自计心用。

RDB/CSB: Pin22,并行模式下的写控制端,与串行模式片选端复用。

FSK/BPSK/HOLD: Pin29,多功能复用引脚。FSK工作模式下,低电平选择频率F1,高电平选F2; BPSK模式时,低电平选相位1,高电平选相位2 ; Chirp模式时,高电平使DDS输出保持当前频率。

SHAPED KEYING: Pin30,高电平使DDS输出有一个调幅过程,若电路设计为低电平,DDS将没有输出。

VOUT: Pin36,高速比较器输出端。

VINP: Pin42,比较器正电压输入端。

VINN: Pin43,比较器负电压输入端。

IOUTl: Pin48,余弦DAC单极电流输出端。

IOUTIB: Pin49,余弦DAC单极电流互补输出端。

IOUT2B : Pins 51,控制DAC单极电流互补输出端。

IOUT2: Pin52,控制DAC单极电流输出端。

DACBP: Pin55, DAC旁路电容连接端。从该端口串接一0.01 uF电容到AVDD可以改变SFDR性能。

DAC RSET: Pin56, DAC满幅输出设置:RSET=39.9/IouT。

PLL FILTER: Pin61,串接1.3k电阻和0.01 uF到AVDD(Pin60),构成参考源倍频PLL环路滤波器的零补偿网络。

DIFF CLK: Pin64,差分时钟使能端,高电平有效。AD9852的时钟输入有两种方式:单端正弦输入和差分输入,具体采用哪一种方式,通过它来选择。

REFCLKB: Pin68,差分时钟的互补输入端。

REFCLK: Pin69,单端时钟信号输入或差分时钟的另一输入端。

S/P SELECT: Pin70,编程模式选择端。逻辑高选择并行模式。

MASTER RESET: Pin71AD9852的复位端,持续 10个系统时钟周期的高电平可以准确复位,内部寄存器的状态为缺省状态。

安可林文章网新闻资讯

安可林文章网新闻资讯